PCI Express is based on a serial protocol, which means that the interface can use a very small number of connectors. In doing so, the PCIe connections are clocked faster than the parallel busses (PCI, AGP) in order to obtain a high bandwidth.

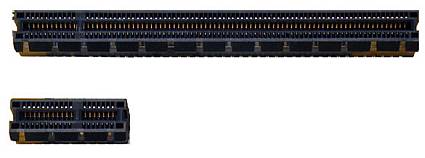

The bandwidth can be multiplied by merging several PCI Express lanes. The specification provides for five different slot types: x16, x8, x4, x2 and x1.

PCI Express is a bi-directional point-to-point link. This means that it offers the same bandwidth in both directions and it does not need to share its bandwidth with other devices, as is the case with parallel PCI.

Due to its modular architecture, motherboard makers are able to distribute the available PCI Express resources to their preferred slot configuration. With a total of 20 PCI Express lanes per motherboard, they can be arranged as one x16 PCIe slot and four x1 PCIe slots, which is a common practice with many chipsets.

Alternately, five x4 PCIe ports can be implemented for mid-range server systems. Whatever is mathematically doable can be implemented with PCI Express. Also, PCI Express could make it possible to mix chipset components from different manufacturers.

PCI Express has one major disadvantage. The more PCIe lanes on a motherboard, the higher the power consumption. This is the biggest reason why chipsets with 40 or more PCIe lanes require considerably more power than products with a smaller number of lanes. By adding 16 additional PCIe lanes the power requirements are raised by about 10 Watts.